声明: 本文根据公开信息整理,所有内容不构成投资建议,股市有风险,投资需谨慎。

日前有媒体报道称,由于AI领域算力需求增长,英伟达、博通、AMD 都在争抢台积电 CoWoS 产能,强劲追单动能更已延续至 2024 年,整体下单规模较 2023 年至少再增 2 成以上。台积电为了满足源源不断的需求,正在积极扩展CoWoS封装产能,计划到 2023 年年底,将 CoWoS 封装月产能从 8000 片提升到 11000 片晶圆,到 2024 年年底增加到 14500-16600 片晶圆。

如果说AI涌现的瓶颈在于算力,那么当前算力竞赛最主要的瓶颈就是CoWoS产能。

一、什么是CoWoS?

CoWoS是台积电2.5D封装技术的代表。证通社去年8月《【热点解析】Chiplet破局芯片国产替代瓶颈 封测设备千亿版图重构(产业链解析) 》一文曾介绍过CoWoS。

传统的芯片生产,是先装再封,从晶圆(Wafer)上切割下来的裸片(Die),放到基板(Sustrate)上,引出管脚/引线,再将其固定、封装进一个外壳中,才能应用于实际的电路中。在先进封装技术出现之前,芯片制程紧跟摩尔定律的路线图,从600nm一路狂奔到了65nm,但芯片之间封装的金属间距(Metal Pitch)却停留在110um,长达20年没有进步。封装技术无法跟上摩尔定理的脚步。

2011年,台积电宣布将会做先进封装,并经过两年时间,台积电开发出了CoWoS(Chip On Wafer On Substrate)技术。

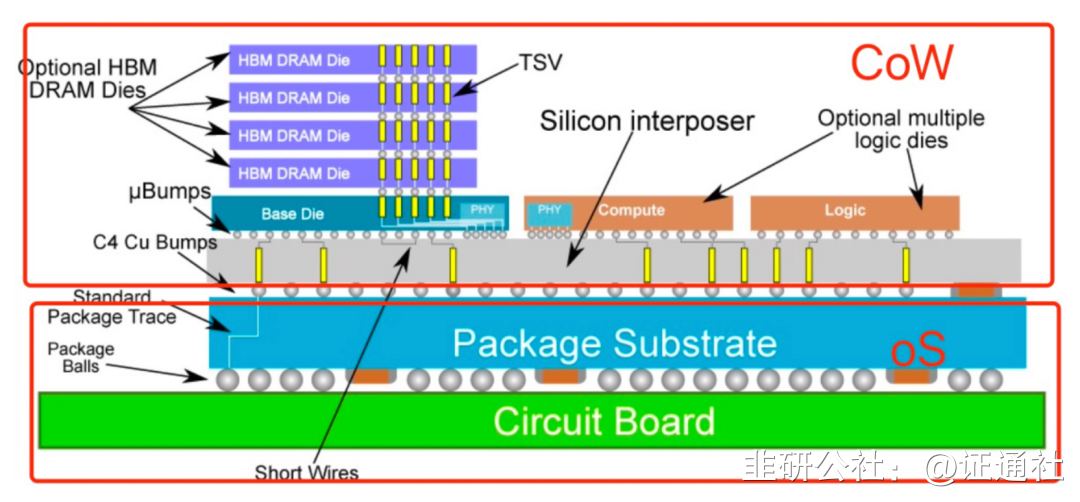

简单来说,CoWoS包含两部分,先通过“CoW”(Chip on Wafer)把不同的芯片(像是处理器、记忆体等)连接到硅晶圆制作的中介层(Silicon interposer),然后再通过“oS”(on Substrate)与封装底衬(Package Substrate)连接。利用这种封装模式,使得多颗芯片可以封装到一起,透过Si Interposer 互联,达到了封装体积小,功耗低,引脚少的效果。

与其他类似的技术相比,台积电CoWoS的突出优势体现在连接裸片的方式:装载裸片的晶圆被台积电称为硅中介层,在硅中介层中,台积电使用微凸块(ubmps)、重新布线(RDL)等技术,代替了传统引线键合用于裸片间连接,并以硅穿孔(TSV,Through-Silicon Via)连接上下的金属层,克服传统封装难以高密度布线的难题,大 大提高了互联密度以及数据传输带宽。

二、为什么现在CoWoS爆发?

CoWoS价格昂贵,最初只有Xilinx使用,为了拿下苹果这个客户,台积电开发出了一种精简的设计,能够将CoWoS结构尽量简化,并且价格压到原来的五分之一。这个技术就是后来的InFO技术。自此,台积电的先进封装分成了两部分,更为经济的InFO封装技术,成为收集客户采用的首选,这也是台积电拿下苹果这个客户的原因。而专注于高阶客户市场的CoWoS技术也因为AI的发展,得到进一步发展与应用。

随着AI训练模型发展,尤其是ChatGPT横空出世,算力需求急剧增加,AI 处理器架构带宽瓶颈出现,也就是 IO 问题。要解决这个问题需要付出很高的代价(比如增加 DDR 接口通道数量、片内缓存容量、多芯片互联),这边催生了HBM的应用。HBM(High Bandwidth Memory)意为高带宽存储器,具有高吞吐高带宽的特性,它单颗粒的带宽可以达到 256 GB/s,远超过 DDR4 和 GDDR6。

HBM和CoWoS是相辅相成的。HBM的高焊盘数和短迹线长度要求需要2.5D先进封装技术,如CoWoS,以实现这种密集的短连接,这在PCB甚至封装基板上是无法实现的。CoWoS是主流封装技术,以合理的成本提供最高的互连密度和最大的封装尺寸。由于目前几乎所有的HBM系统都封装在CoWos上,所有先进的人工智能加速器都使用HBM,因此几乎所有领先的数据中心GPU都是台积电封装在CoWos上的。

三、CoWoS的变体与发展

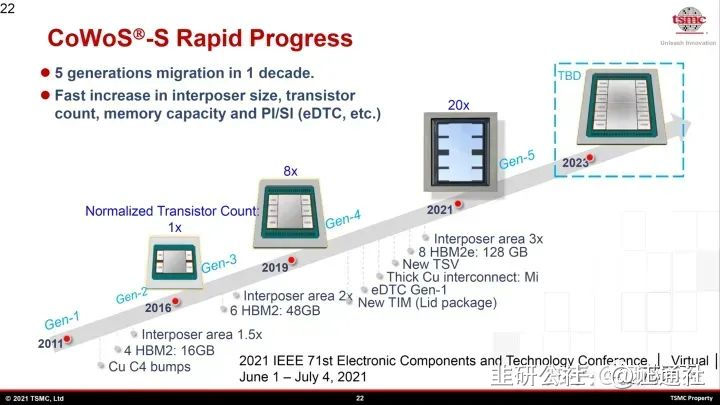

CoWoS有几种变体,但原始CoWoS-S仍然是大批量生产中的唯一配置。这是如上所述的经典配置:逻辑芯片+HBM芯片通过带有TSV的硅基中介层连接。然后将中介层放置在有机封装基板上。

硅中介层的一项支持技术是一种称为“reticle stitching”的技术。由于光刻工具slit/scan*尺寸芯片的*尺寸通常为26mm x 33mm 。随着 GPU 芯片本身接近这一极限,并且还需要在其周围安装 HBM,中介层需要很大,并且将远远超出这一标线极限。TSMC 通过reticle stitching解决了这个问题,这使得他们能够将中介层图案化为标线限制的数倍(截至目前,AMD MI300 最高可达 3.5 倍)。

去年,台积电将他们的 2.5D 和 3D 封装产品合并为3DFabric。其中,2.5D封装技术CoWoS可分为 CoWoS 和 InFO 系列,3D封装技术则是SoIC。据台积电介绍,2.5D CoWoS® 平台可为人工智能、机器学习和数据中心等 HPC 应用集成高级逻辑和高带宽内存。InFO PoP 和 InFO-3D 支持移动应用,InFO-2.5D 支持 HPC chiplet 集成。SoIC 是一种台积电创新的多芯片堆栈技术,能对 10nm 以下的制程进行晶圆级的接合技术。通过硅通孔(TSV)使得该技术没有突起的键合结构,因此有更佳的性能。SoIC 堆叠芯片可以集成到 InFO 或 CoWoS 封装中,以实现最终系统集成。

四、大陆的先进封装

市场机构监测数据显示,2022年全球先进封装的收入增长了约10%。2022年价值443亿美元,预计2022—2028年复合年增长率(CAGR)为10.6%,到2028年达到786亿美元。先进封装已成为半导体创新、增强功能、性能和成本效益的关键。

中国大陆承担了全球封测近20%产能,头部厂商在先进封装的开发上也并不落后。例如全球第三、中国大陆第一的封测厂长电科技,已经开发了2.5D/3D封装、晶圆级封装(WLP)、堆叠封装(PoP)等先进封装技术,覆盖面可追平日月光。全球第五、中国大陆第二的通富微电,除了掌握2.5D/3D封装等技术外,还在收购了AMD两大封测厂后与其深度绑定,后者是目前先进封装的最大客户之一。

有别于传统封装,先进封装还需要不同的设备、材料和工艺,例如新的基板材料、光刻工艺、激光钻孔、CMP 和 KGD 测试,涉及到RDL(再布线)、TSV(硅通孔)、Bump(凸块),Wafer(晶圆)等等要素。国内产业链还需要有非常多的细节需要突破。

- 1

- 2

- 3

- 4